# 1U ラックマウント型 98%効率整流器の開発

## Development of 1U rack-mount 98% efficient rectifier

石 倉 啓 太\* 千 葉 明 輝\*

Keita Ishikura Akiteru Chiba

### Abstract

A 1U rack-mount telecom rectifier with single phase AC input and a 2 kW / 54 V DC output is developed, achieving 98% peak efficiency. This rectifier integrates a >99% efficient ZVS CrM interleaved totem-pole bridgeless PFC with an existing three phase LLC resonant converter (>99%). This paper mainly focuses on PFC designs. A simple, noise robust zero current detection scheme is unveiled, enabling ZVS across the full AC input voltage range. And only Si devices are used.

*Key words :* 98% efficient rectifier, ZVS and interleave, totem-pole PFC, integrated inductor

## 1 はじめに

現代社会が直面している気候変動や資源枯渇などの課題に対応するため、国際社会は SDGs（持続可能な開発目標）を掲げ、持続的かつ強靭な社会・経済構造の構築に取り組んでいる。とくに SDGs 目標 7「エネルギーをみんなに、そしてクリーンに」と目標 13「気候変動に具体的な対策を」の達成には、エネルギー利用の効率化が不可欠である。このような背景の中、急増するデータセンターや通信基地局用の電源ユニットは高効率化が要望されている。エネルギー消費と運用コストの削減に直結するためである。

今回、通信基地局用の整流器に搭載する臨界導通モードインターブルートーテムポール PFC を開発した。シンプルでノイズに強いゼロ電流検出回路と、全入力電圧範囲でのゼロ電圧スイッチング制御を提案し、Si 半導体のみで最大効率 99%超を達成した。すでに開

発済みの効率 99%超の 3 相マルチフェーズ LLC 電流共振コンバータ<sup>1,2</sup>と組み合わせ、整流器全体効率は 98%を実現した。

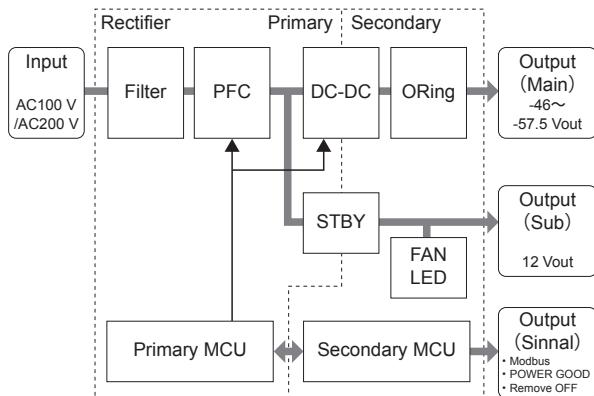

## 2 主回路

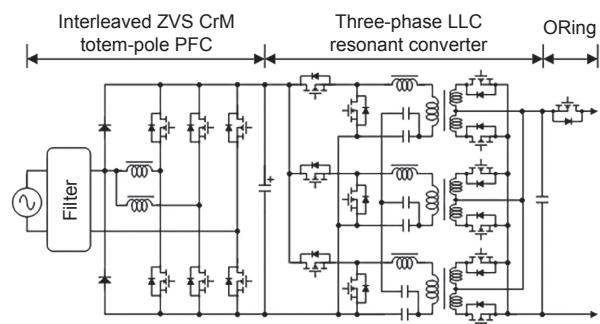

Fig. 1 に主回路構成を示す。AC / DC 変換をおこなう PFC と、DC / DC 変換をおこなう LLC コンバータとを備える。

Fig. 1 Main circuit configuration.

\* 電源システム開発本部 先端開発部 第二 G

## 2.1 PFC（効率改善回路）

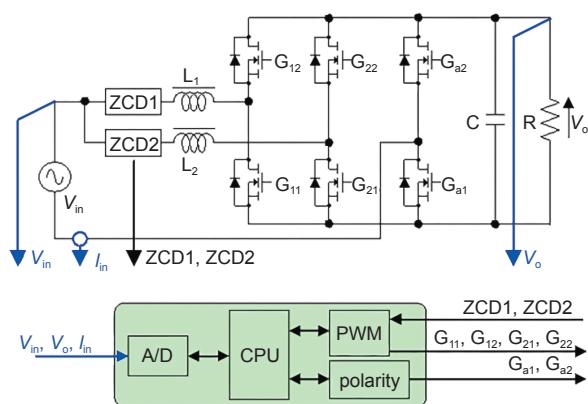

Fig. 2 にあるように、高効率化と大電力対応のためには臨界導通モード (CrM) インターリーブトーテムポール PFC を採用している。さらに安定した効率向上を得る手法の一部を紹介する。シンプルでノイズに強い低損失 ZCD 回路、全入力電圧範囲で ZVS を実現する制御方法、周波数変調下でも素子ばらつきに依存せず位相差  $180^\circ$  を自動維持する方法である。これらをデジタル制御で実現し、ZVS によりターンオン損失を最小化してスイッチング損失を大幅に低減し、効率を向上させる。そして統合リアクトルは磁気相殺により損失を抑え、GaN や SiC を用いず Si 半導体のみで最大効率 99% 超を達成した。

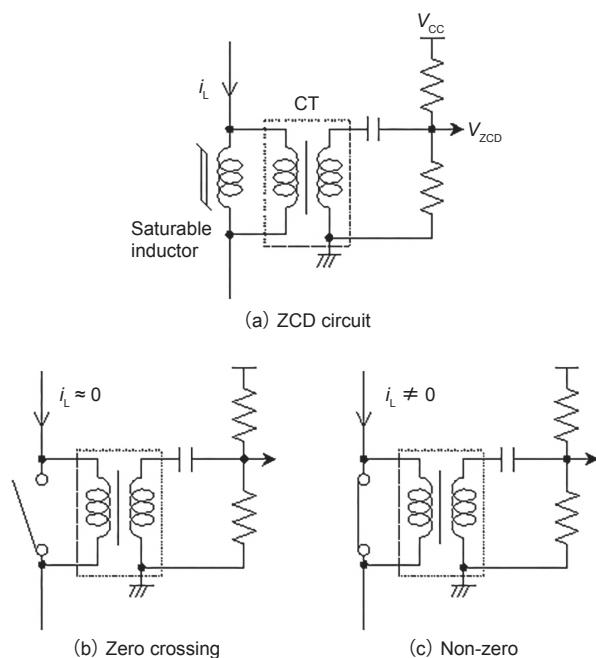

### 2.1.1 ZCD (Zero Current Detection) 回路

次節で述べる全入力電圧範囲での ZVS のために、リアクトル電流を入力側へ回生し、回生電流はリアクトル電流のゼロ検出から決定される。

Fig. 3(a) の ZCD 回路を提案した<sup>3</sup>。可飽和リアクトルと CT (Current Transformer) の並列接続で構成される。原理的な考え方として、0 A 付近での可飽和リアクトルは大きなインダクタンス成分を持つため、等価的にスイッチオープン状態になり CT の 1 次側に電流が流れ、2 次側でゼロ電流を示す  $V_{ZCD}$  を得る。一方、0 A 以外では可飽和リアクトルの磁気飽和により、等価的にスイッチショート状態となって、CT に作用しない。

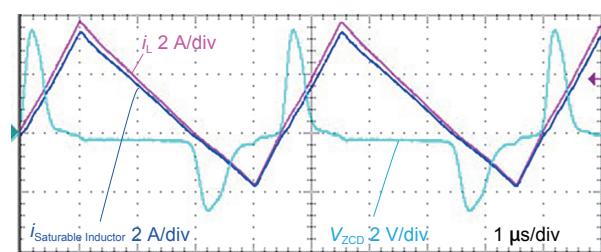

Fig. 4 に ZCD 回路の動作波形を示す。リアクトル電流  $i_L$  のゼロクロスタイミングで ZCD 回路の  $V_{ZCD}$  は急峻に変化している。 $V_{ZCD}$  は MCU に取り込まれ、エッジ検出して ZVS 制御に利用される。

Fig. 2 Interleaved CrM totem-pole PFC with MCU.

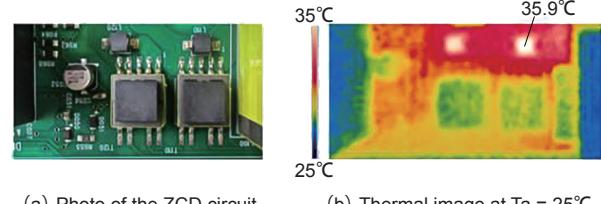

Fig. 5 に ZCD 回路周辺の温度測定結果を示す。定格入出力時の温度上昇は  $10^\circ\text{C}$  程度であった。すなわちジュール熱は小さく、低損失であることがわかる。また抵抗の電圧降下を検出する電流検出回路と比べて導通損失を低減できる。加えて電流駆動型の回路構成であるため、耐ノイズ性が強いという特長を併せ持っている。

Fig. 3 ZCD circuit and operating principle.

Fig. 4 ZCD operating waveforms.

Fig. 5 Operating temperature of the ZCD circuit.

### 2.1.2 ZVS (Zero Voltage Switching)

スイッチング損失を最小限に抑えるためにZCD回路と回生電流により、全入力電圧範囲において主半導体をゼロ電圧状態でターンオン（ZVS）させる。

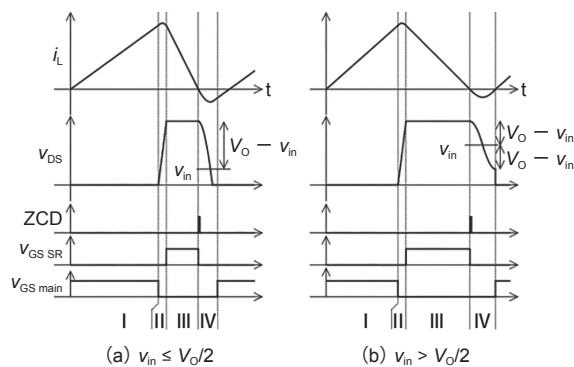

Fig. 6に従来のCrM PFC動作を示す。 $v_{in} \leq V_0/2$ の領域では自然にZVSできるが、 $v_{in} > V_0/2$ ではZVSできずハードスイッチングしてしまう。これは、期間IVにおける主半導体の $v_{DS}$ が、 $v_{in}$ 点を中心に振幅 $V_0 - v_{in}$ の電圧共振をするためである。

Fig. 7では期間I～IVまでの1スイッチングサイクルの挙動を $i_L - v_{DS}$ 平面で表した。 $i_L$ は特性インピーダンス $Z_C = \sqrt{L/(2C_{oss})}$ で規格化した。

$v_{in} > V_0/2$ の領域でもZVSするためには、リアクトル電流 $i_L$ を入力側に回生する必要がある。

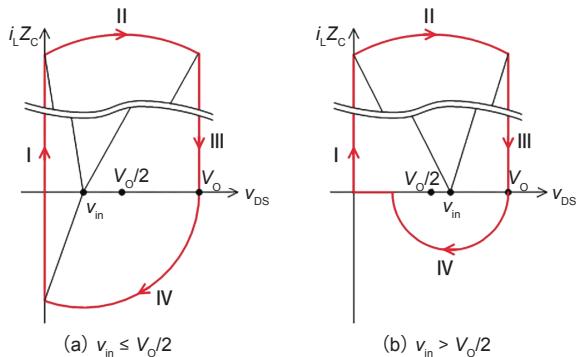

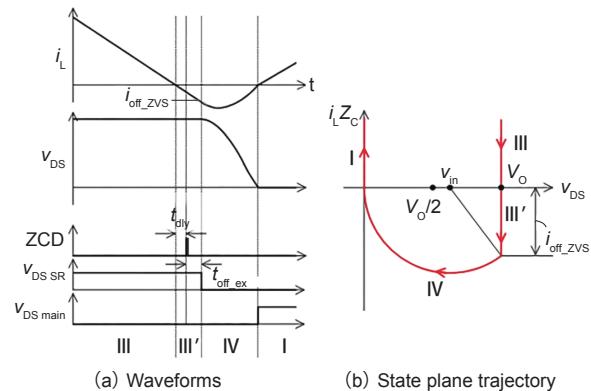

Fig. 8に電流を回生した場合の回路波形と $i_L - v_{DS}$ 平面図を示す。期間III'の意図的な回生電流は、期間IVの共振振幅を大きくしZVS可能なことを示す。回生電流 $i_{off\_ZVS}$ はFig. 8(b)から幾何学的に計算できる。

$$i_{off\_ZVS} = \begin{cases} 0 & v_{in} \leq V_0/2 \\ -\frac{\sqrt{(2v_{in}-V_0)V_0}}{Z_C} & v_{in} > V_0/2 \end{cases} \quad (1)$$

Fig. 6 Theoretical waveforms of CrM PFC.

Fig. 7 State plane trajectories of  $i_L$  and  $v_{DS}$ .

Fig. 8(a)が示す電流ゼロクロスからZCD信号までのわずかな遅れ時間 $t_{dly}$ は、補正量としてMCU内で回生時間 $t_{off\_ex}$ の計算に加味される。

$$t_{off\_ex} = |i_{off\_ZVS}| \cdot \frac{L}{V_0 - v_{in}} - t_{dly} \quad v_{in} > V_0/2 \quad (2)$$

これらの制御が全入力電圧範囲でZVSを可能にする。

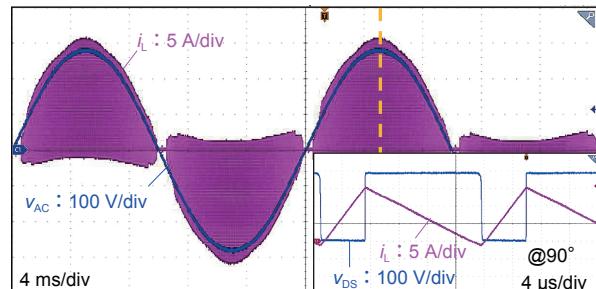

Fig. 9に定格入出力時のAC周期と位相90°でのスイッチング波形として示す。計算された回生時間による回生電流がZVSを実現している。

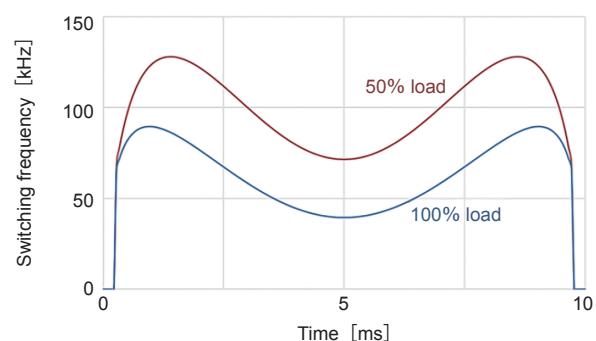

Fig. 10にFig. 9の半AC周期におけるスイッチング電流の動作周波数分布を示す。

Fig. 8 Principle of ZVS control when  $v_{in} > V_0/2$ .

Fig. 9 Waveforms at full load.

Fig. 10 Calculated switching frequency distribution.

### 2.1.3 インタリープ制御

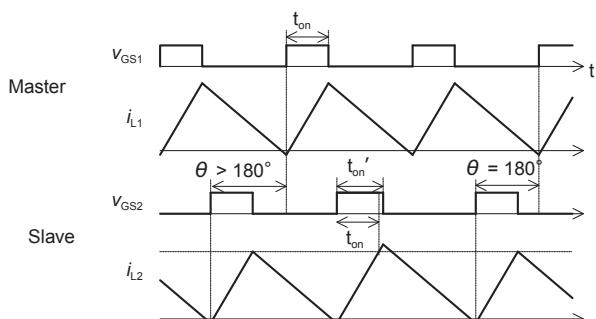

主回路を並列接続した  $180^\circ$  位相差でのインタリープは、高効率化と大電力対応に加え、入力リップル電流低減にも貢献する。ゆえに周波数変調の CrM PFC では、素子などのばらつきがあっても常に適切なインタリープを維持することがひとつの課題である。

Fig. 11 のように 1 相目をマスター相、2 相目をスレーブ相として、2 相目のオン時間調整するインタリープ制御を行っている。

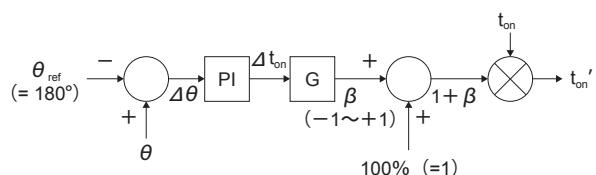

Fig. 12 に制御ブロック図を示す<sup>4</sup>。1 相目と 2 相目の位相差  $\theta$  を計測し、目標位相差 ( $180^\circ$ ) となるよう偏差を抑える方向にオン時間補正值  $\Delta t_{on}$  を算出する。この  $\Delta t_{on}$  にもとづく補正率 ( $1 + \beta$ ) を基準となるオン時間  $t_{on}$  に乗算する。

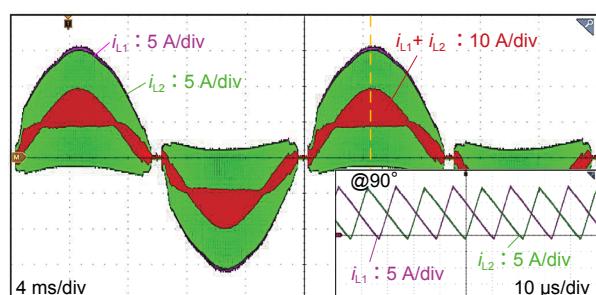

Fig. 13 に 1 相目と 2 相目のリアクトル電流波形を示す。 $180^\circ$  の位相差を維持したインタリープを実現している。合成電流波形のリップルは各相の電流と比べ大きく低減していることも確認できる。

Fig. 11 Principle of two-phase interleaving.

Fig. 12 Block diagram of interleaving control.

Fig. 13 Inductor current waveforms at full load.

### 2.1.4 統合リアクトル

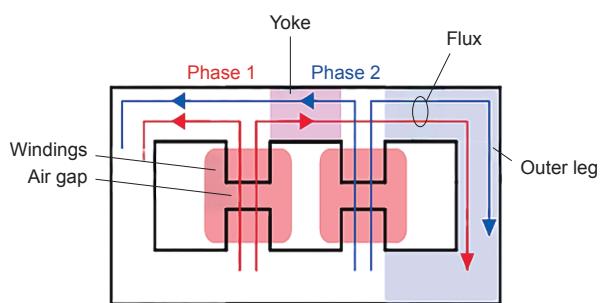

Fig. 14 にリアクトルの鉄芯と巻線の構成を示す。2つのリアクトルを統合して 4 脚構成とした。鉄芯とエアギャップの透磁率差により、各相の中脚を出た磁束の大部分は左右に分流してギャップレスの外脚を通り、各相どうしあわざかに磁気結合する。

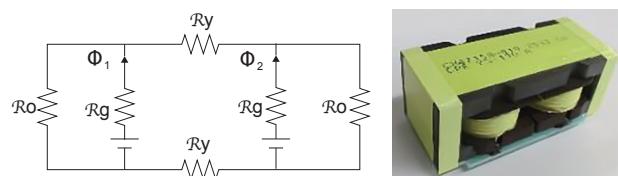

Fig. 15 に統合リアクトルの磁気回路を示す。 $R_o$ ,  $R_y$ ,  $R_g$  は順に外脚、天板、エアギャップの磁気抵抗とし、 $R_o$ ,  $R_y \ll R_g$  である。各相の中脚を出た磁束は磁気抵抗により分流し、外脚と天板で合成される。

Fig. 16 に 4 脚リアクトルの外観を示す。

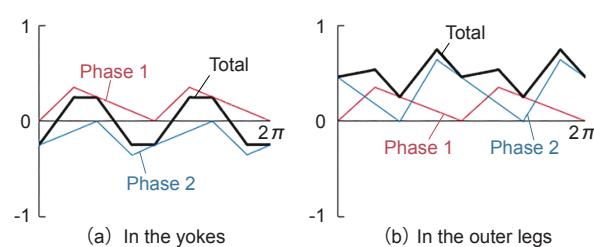

Fig. 17 に統合リアクトル鉄芯の磁束波形を示す。デューティ 0.3 を仮定し、中脚で生じる磁束を 1 として正規化している。天板、外脚の磁束は相殺されて各中脚の磁束よりも低減するため、鉄損低減できる。また、外脚の合成磁束は 2 倍の周波数成分を持つため周波数依存性の鉄損増大が懸念されるが、外脚の断面積や形状を考慮することで回避している。

Fig. 14 Four-legged two-winding structure.

Fig. 15 Magnetic circuit.

Fig. 16 Integrated inductor.

Fig. 17 Magnetic fluxes in the core.

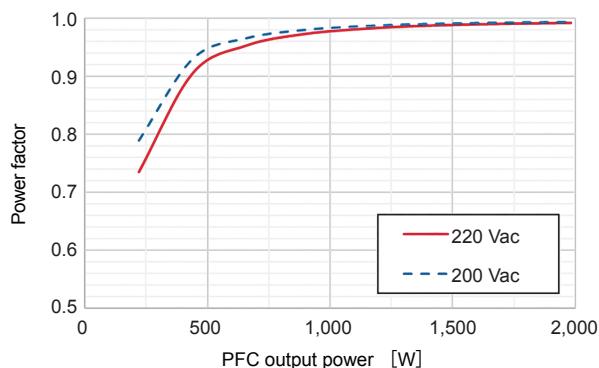

### 2.1.5 PFCの効率と効率

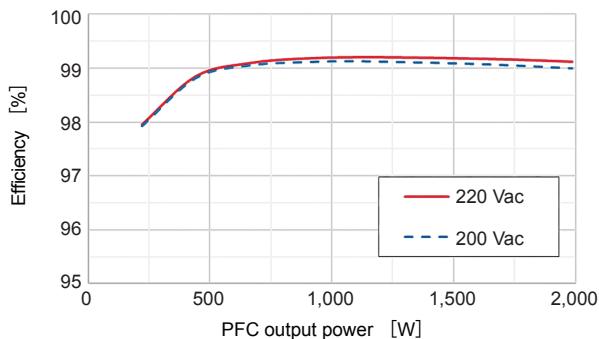

Fig. 18に効率を示す。保持時間10 msを得るために出力平滑コンデンサは680 μFとした。広い負荷範囲で効率0.99以上を確保できている。

Fig. 19は入力フィルタを含んだ変換効率を示す。広い負荷範囲で効率99%を超える、最大効率99.20%を達成した。GaNやSiCを使用せずSi-MOSFET（東芝製TK095V65Z5）を用いている。

これまで述べたように、シンプルで低損失なゼロ電流検出回路（ZCD）、全入力電圧範囲でのゼロ電圧スイッチング（ZVS）動作、自動インターブル制御と、これらを統括するデジタル制御、そして磁気統合リアクトルによって99%超の高効率を達成している。

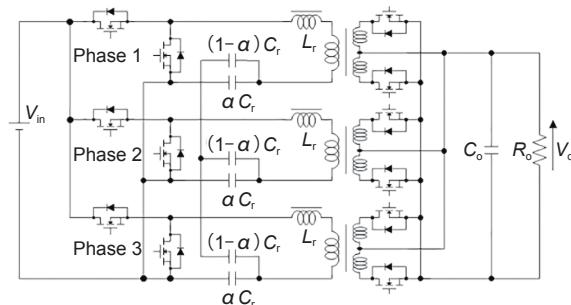

### 2.2 絶縁DCDCコンバータ

Fig. 20に示す3相マルチフェーズLLC電流共振コンバータ（3相LLC）はすでに効率99%超として開発されている<sup>1,2</sup>。簡単に紹介する。

共振コンデンサ $C_r$ を2分割したハーフブリッジLLCコンバータを単位回路として3並列接続し、 $\alpha C_r$ は電源ラインに接続され、 $(1-\alpha) C_r$ は他相と相互接続されて中性点を形成する。 $0 \leq \alpha \leq 1$ とする。

3相LLCの共振角周波数 $\omega_r$ は次式で与えられる。

Fig. 18 PFC power factor.

Fig. 19 PFC efficiency.

$$\omega_r = \frac{1}{\sqrt{L_r \{ \alpha C_r + (1-\alpha) C_r \}}} = \frac{1}{\sqrt{L_r C_r}} \quad (3)$$

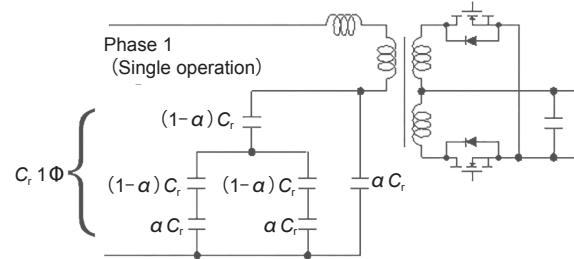

また出力電力に応じて相数を可変できる優位性を備える<sup>2,5</sup>。軽負荷時では1相動作、中重負荷では3相動作に動作相数を変えて軽負荷時効率を確保する。

Fig. 21に1相動作時の共振コンデンサの接続を示す。ひとつの共振コンデンサ $C_r 1\phi$ として機能する。

$$C_r 1\phi = \frac{3}{2\alpha+1} C_r \quad (4)$$

共振コンデンサ $C_r$ は電流平衡能力と調達性から分割比 $\alpha = 0.5$ とした。1相動作時の共振角周波数とスイッチング周波数の増分は約15%になる。

$$\Delta f_s = \sqrt{\frac{2\alpha+1}{3\alpha}} - 1 = \sqrt{\frac{2 \cdot 0.5+1}{3 \cdot 0.5}} - 1 = 0.15 \quad (5)$$

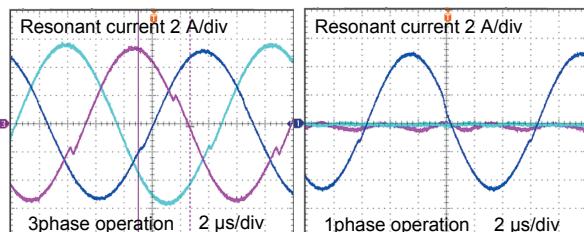

Fig. 22は共振電流波形である。3相動作の共振電流は平衡しており、単相動作も実現している。

Fig. 20 Three-phase LLC resonant converter.

Fig. 21 Equivalent resonant capacitor  $C_r 1\phi$ .

Fig. 22 Current waveforms.

Fig. 23 Three-phase LLC converter efficiency.

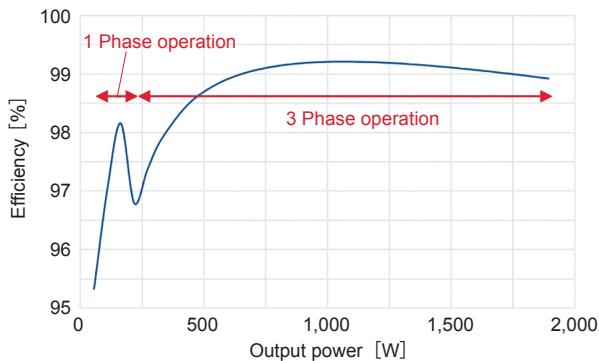

Fig. 23 は 3 相 LLC の効率特性である。1 相／3 相動作は 200 W 出力付近でヒステリシス幅を持って切り替わる。広い出力範囲で効率 99% を超えており、最大効率 99.2% を獲得している。

### 3 整流器

Table 1 に整流器の仕様を示す。

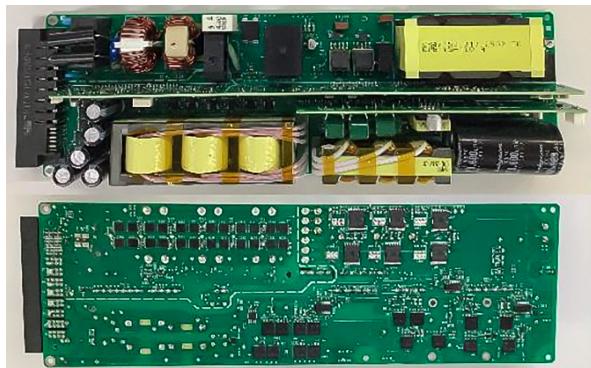

Fig. 24 は PFC および 3 相 LLC を搭載した基板の外観である。表面は受動部品が主体であり、制御部・補助電源は子基板実装、裏面に主半導体を SMD 実装している。4 層基板を使用した。

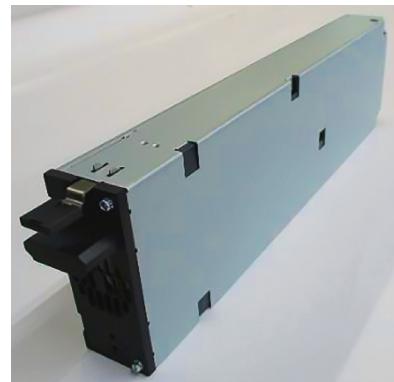

Fig. 25 は FAN を搭載した鉄ケースに収めた外観である。主半導体は基板ウラ面とケース間の微風のみで放熱し、放熱フィン不要によりコスト抑制する。

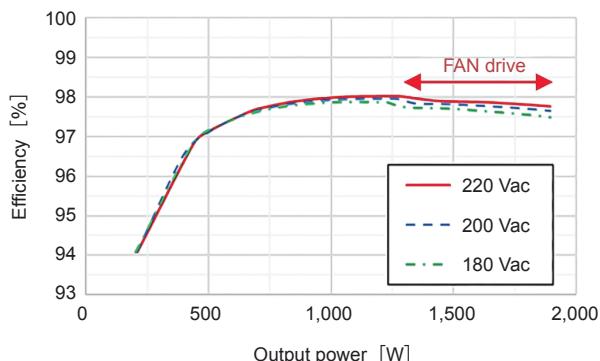

Fig. 26 に示すシステム概要のとおり、主回路に加え補助電源、通信、電力マネジメント、FAN 駆動を備える。これら出力に寄与しない回路を搭載しつつ、Fig. 27 のとおり最大総合効率 98% を達成した。

Table 1 Specifications.

| Parameter              | Value                            |

|------------------------|----------------------------------|

| Input Voltage          | 1 φ AC90 ~ 110 V / AC180 ~ 220 V |

| Peak Efficiency        | 98%                              |

| Power Factor           | >0.99 @Rated output              |

| Output Voltage         | -46 ~ -57.5 V                    |

| Output Current         | 0 ~ 35 A                         |

| Current Protection     | ≤ 110%                           |

| Ripple Voltage         | ≤ 200 mVp-p                      |

| Operation Temp.        | -10 ~ +45°C                      |

| EMI                    | VCCI class A compliant           |

| Interface              | POWER GOOD, Remote OFF           |

| Communication Protocol | Modbus                           |

Fig. 24 Rectifier board.

Fig. 25 Outside view.

Fig. 26 Rectifier block diagram.

Fig. 27 Rectifier efficiency.

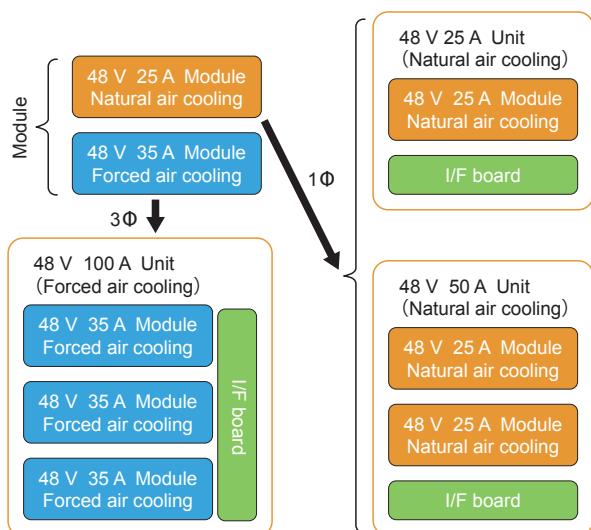

Fig. 28 Module expansion portfolio (excerpt)<sup>1)</sup>.

#### 4 製品展開ポートフォリオ

モジュラーデザインと呼ばれる設計手法導入にも取り組んでいる。今回開発した整流器にも機能、仕様、インターフェイスなど他製品との互換性を持たせた。

Fig. 28 はすでに製品化されている総合効率 96% の AC-DC モジュール製品<sup>1)</sup>の製品展開ポートフォリオから抜粋したものである。ここに今回開発した整流器も組み込まれる。開発期間短縮や設計工数削減、部品共通化によるコスト削減や調達性改善を図る。

また総合効率 98% を獲得したことで、これまで出荷してきた AC-DC モジュール群に本整流器を適用すれば、CO<sub>2</sub> 排出量は年間 1,200 t の削減ができる (CO<sub>2</sub> 排出量換算係数 : 電気 0.423 t-CO<sub>2</sub> / MWh として 1 万台に適用した場合)。

#### 5 まとめ

通信基地局用の整流器に搭載する高効率な PFC を開発した。低損失な ZCD 回路や全入力電圧範囲での ZVS 動作とインタリープ制御、そして鉄損を低減する統合リアクトルの提案によって、PFC は 99% 超の高効率を実現した。また開発済みの効率 99% 超の 3 相マルチフェーズ LLC 電流共振コンバータと組み合わせて、整流器全体効率 98% を達成した。

今回培った技術を他製品にも展開するとともに、本技術を追求し、さらなる小型化、高効率化を目指す。エネルギー効率を追求した製品開発を通じ、強靭かつ持続可能な社会の構築に貢献していきたい。

#### 参考文献

1. 西山 利行, 宮原 隆浩, 宮田 智弘, 宮崎 伊佐夫, 「高効率 AC-DC モジュールの製品化」, GS Yuasa Technical Report, **20** (1), 9 (2023).

2. 千葉明輝 他, 「効率 99%, 5W/cc の三相 LLC 電流共振型コンバータ」, サンケン技報, **52**, 48 (2020).

3. GS ユアサ, 千葉明輝, ゼロ電流センサ及び電源回路, 特願 2024-130867.

4. GS ユアサ, 石倉啓太, 永野史弥, 電力変換器, 充電装置, 車両, 電源装置, 力率改善回路, DC – DC コンバータおよびインバータ, 特開 2025-142604.

5. GS ユアサ, 千葉明輝, 3 相 LLC コンバータ, 特許第 7501341 号.

6. GS ユアサ, 千葉明輝, 石倉啓太, 力率改善回路, 特許第 7501267 号.

7. GS ユアサ, 千葉明輝, 石倉啓太, 力率改善回路, 特許第 7768296 号.

8. A. Chiba, K. Ishikura et al., "The Potential of LLC Resonant Converters Equipped With Split Resonant Capacitors: From Three-Phase to Fractal Structures", Proc. IEEE Int. Power Electron. Conf., 1711 (2022).