# 報文

# ミニ UPS インバータへのデジタル制御の適用

# Application of Digital Control Scheme for Mini UPS Inverter

坂 根 誠\* 劉 亜 東\*\* 邢 岩\*\*\* 黄 立 培\*\* 平 地 克 也\*\*\*\*

> Makoto Sakane Yadong Liu Yan Xing Lipei Huang Katsuya Hirachi

#### Abstract

The digital PID control system has been developed for the inverter of mini-UPS that requires high-speed and cheap CPU. An experimental system was constructed with a main circuit of "YUMIC-SC10" and a digital control circuit consisted of an interface board and a CPU board. The results of simulation and experiments with the system revealed that the control performance was improved by the compensation of the dead time error at steady state and the output current compensation with the rectifier load, while the performance was sensitively decreased at smaller sampling frequencies.

#### 1 はじめに

インバータのデジタル制御は、モーター制御用には広く実用化されているが、無停電電源装置(UPS)用にはあまり普及していない。後者用インバータは、前者のような複雑な周波数や電圧の制御は不要なかわりに、高速で制御をおこなう必要がある。それを担う高速 CPU は高価なので、低価格が要求される UPS、とくにミニ UPS の分野ではデジタル制御はあまり普及していなかった。しかしながら、近年、CPU の高速化と低価格化が進んでいることから、今後はこの分野

\*株式会社ジーエス・ユアサパワーエレクトロニクス

でもデジタル制御の実用化が期待される. その UPS 用インバータのデジタル制御には、PID、デッドビート、スライディングモードおよび、ファジー制御などが考えられる. 本報告は、最も実用的で制御性能が信頼される PID 制御を採用して、シミュレーションと実験とをおこなってデジタル制御のミニ UPS への適用を検証した結果について述べたものである.

# 2 デジタル PID 制御の適用

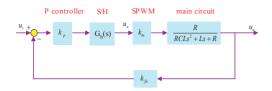

従来のアナログ方式の UPS 用インバータの制御を、デジタル方式に置き換えた場合の制御ブロック図を Fig. 1 に示す。 Gh(s) は、デジタル制御に必須のサンプリング回路の伝達関数である。この回路の遅延時間のために、UPS 用インバータの出力電圧制御の安定性が損なわれる。今回の実験で使用する当社の

<sup>\*\*</sup> 清華大学

<sup>\*\*\*</sup> 南京航空航天大学

<sup>\*\*\*\*</sup> 国立舞鶴高専

Fig. 1 Block diagram of a conventional digital control system.

1 kVA ミニ UPS "YUMIC-SC10" のパラメータを用いて伝達関数を計算し、アナログ制御とデジタル制御を比較すると、後者のゲインマージンは 6.8 dB から 2.8 dB に低下し、位相余裕は 25 度から 13 度に減少した. サンプリング周期は、29  $\mu$  sec. で計算した. デジタル制御での安定性を改善するためにつぎの対策を検討した.

- (1)出力電圧制御のフィードバックループに微分要素を追加

- (2) 出力電圧と基準電圧との誤差を指令値とする フィードフォワード補償を追加

また、制御精度を向上させるために、つぎの対策を検討した。

- (3) 制御結果にデッドタイムによる誤差の補償回路 を付加

- (4) インバータ出力電流の微分値のフィードフォ ワード補償を追加

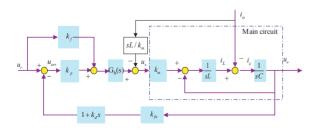

これらの改善を施した制御ブロック図を Fig.2 に示す.

#### 3 実験システム

実験システムは "YUMIC-SC10" の主回路と、インターフェースボードと CPU ボードとからなるデジタル制御回路とで構成した.

Fig. 2 Block diagram of the developed digital control system.

#### 3.1 主回路

"YUMIC-SC10" のインバータ主回路は、ハーフブリッジ形回路を採用した $^{1,2)}$ . 整流器は、PWM 動作はさせずに倍電圧ダイオード整流回路として使用した。

#### 3.2 デジタル制御回路

インターフェースボードでは、出力電圧と出力電流とを検出する。前者は絶縁トランスを介して $\pm$  198 V で、後者はホール CT で $\pm$  30 A で検出され、各々 1.65 V のオフセット電圧を加えた 0 V  $\sim$  3.3 V のアナログ信号(比率 1/120)に変換して、DSP の 10 bit の A/D に出力される。また、CPU は固定小数点汎用 DSP の "TMS320LF2407(2406)A" を使用した。

#### 3.3 DSP のプログラム

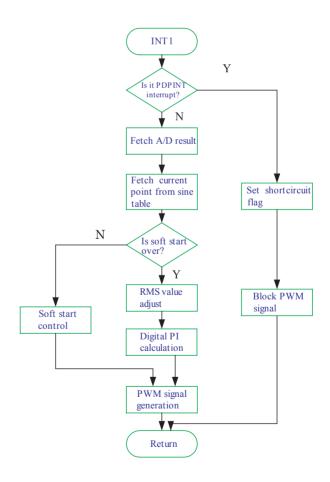

定電圧制御のフローチャート (INT1) を Fig. 3 に 示す. INT1 ルーチンは, 割込で A/D 変換の後に実 行される.

Fig. 3 Flowchart of constant voltage control system.

### 4 シミュレーションと実験

#### 4.1 基礎実験

まず、デッドタイム補償と出力電流補償なしの条件にて、基礎実験とシミュレーションを実施した。サンプリング周波数の影響を調べるために、周波数が34.48 kHz および17.24 kHz での実験をおこなった。

#### 4.1.1 サンプリング周波数 34.48 kHz での実験

シミュレーションと実験に使用したパラメータおよび諸条件を以下に示す。kp, kf, kfu および kdiff は制御のパラメータであり,kdiff は kd とサンプリング周期 t の比 kd/t である。L および C はインバータのLC フィルタの値である。

kp=1.4, kf=0.7, kfu=1/120, kdiff=8

L=1.5 mH, C=20  $\mu$ F

サンプリング周期: t = 0.029 msec.

サンプリング周波数: fs = 34.48 kHz

スイッチング周波数: fsw = 17.24 kHz

出力周波数:50 Hz

デッドタイム時間: Tdead=2 μsec.

DC リンク電圧: ± 170~200 V

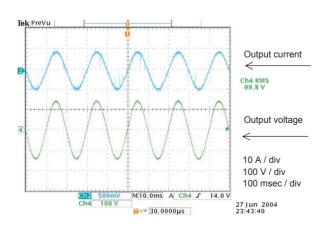

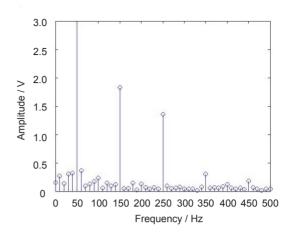

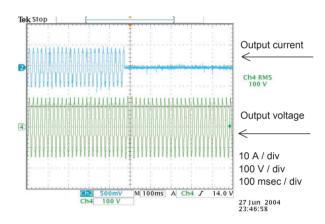

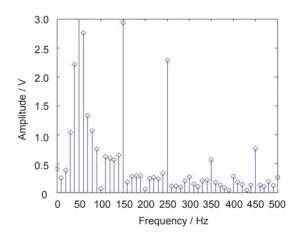

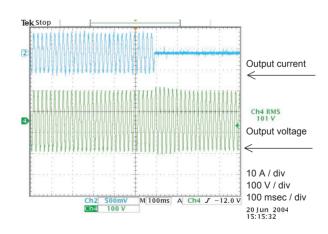

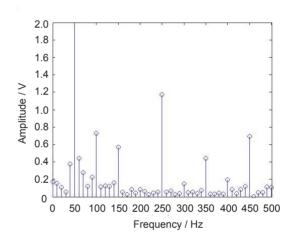

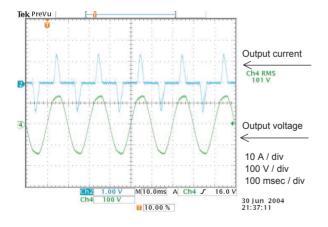

実験システムの定格負荷に相当する 15 Ω負荷時の出力電流・電圧波形および出力電圧の FFT (周波数分析)の実測値を Fig. 4 および Fig. 5 にそれぞれ示す. 15 Ω負荷時の定常状態の電圧は 99.50 V, 基本波は 99.46 V, 歪率は 2.97%であった. 無負荷時の定常状態の出力電圧は 100.075 V, 基本波は 100.0435 V, 歪率は 2.51%であった. つぎに, Fig. 6 および Fig. 7 に. 負荷急変時の出力電圧の過度電圧変動波形を.

Fig. 4 Output voltage and current waveform of 15 ohm resistor load for the test system. Sampling frequency: 34.48 kHz.

Fig. 5 FFT with 15 ohm resistor load for the test system.

Sampling frequency: 34.48 kHz.

Fig. 6 Dynamic response waveform of sudden load change from 100% to 0% for the test system. Sampling frequency: 34.48 kHz.

Fig. 7 Dynamic response waveform of sudden load change from 0% to 100% for the test system. Sampling frequency: 34.48 kHz.

Table 1 CRMS value at sudden load change from 100 % to 0 % for the test system.

| Time / msec  | Before | 20    | 40    | 60    | 80     | 100    |

|--------------|--------|-------|-------|-------|--------|--------|

| RMS value/ V | 99.86  | 106.6 | 105.2 | 103.3 | 100.85 | 100.55 |

Table 2 Change in RMS value at sudden load change from 0 % to 100 % for the test system.

| Time / msec   | Before | 20    | 40    | 60    | 80    | 100    |

|---------------|--------|-------|-------|-------|-------|--------|

| RMS value / V | 100.26 | 92.09 | 94.00 | 96.39 | 98.78 | 100.52 |

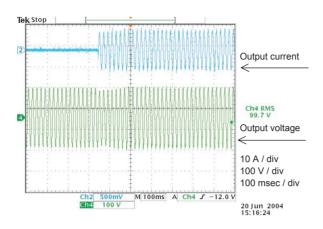

Table 1 および Table 2 に急変後の電圧値を示す.過渡電圧変動率は  $100\% \rightarrow 0\%$ の負荷急変に + 6.75% (整定時間 80 msec.), $0\% \rightarrow 100\%$ のときに - 8.15% (同 100 msec.) であった.

このシステムは、非制御のハーフブリッジのダイオード整流器を使用している。直流リンク電圧 Ud の平均値の変動は、負荷急変後の1サイクル (20 msec.) で5 V であることがわかった。Matlab simulink によって、Ud が変化したときの出力電圧におよぼす影響をシミュレートした。その結果、Ud が5 V 変化したとき、出力電圧の実効値で1.4 V (1.4%)変化して、負荷には関係ないことがわかった。直流リンク電圧 Ud を安定させることによって、出力電圧の変動は1.4%に抑えられることがわかった。

#### 4.1.2 サンプリング周波数 17.24 kHz での実験

シミュレーションと実験に使用したパラメータおよび諸条件を以下に示す. サンプリング周波数を 4.1.1 項の 34.48 kHz から 17.24 kHz に, すなわち周期を 2 倍にすると, インバータの動作が不安定となった. それを安定させるために, 比例制御のパラメータ kp を 1.4 から 0.3 まで減少させ, フィードフォワードのパラメータ kf を 0.7 から 0.9 に増加させた.

kp=0.3, kf=0.9, kfu=1/120, kdiff=8

L=1.5 mH, C=20  $\mu$  F

サンプリング周期 : t = 0.058 msec.

サンプリング周波数 : fs = 17.24 kHz

スイッチング周波数: fsw = 17.24 kHz

出力周波数: 50 Hz

デッドタイム時間: Tdead=2  $\mu$  sec.

DC リンク電圧: ± 170~200 V

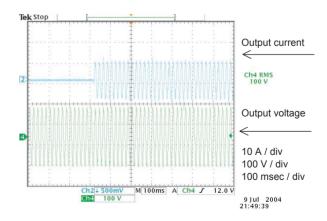

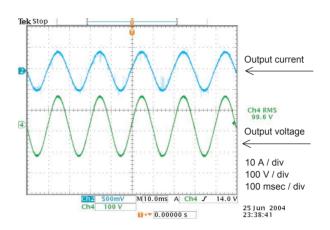

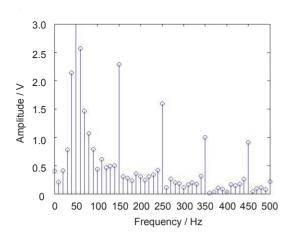

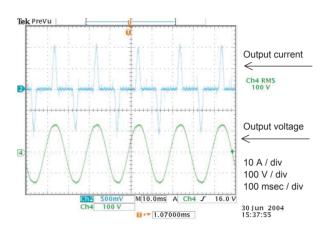

15  $\Omega$ 負荷時の出力電流・電圧波形および出力電圧 の FFT を、Fig. 8 および Fig. 9 にそれぞれ示す。定 常状態の歪率は  $15 \Omega$ 負荷時に 5.0%, 無負荷時に 3.85%

Fig. 8 The output waveform with 15 ohm resistor load for the test system. Sampling frequency: 17.24 kHz.

Fig. 9 FFT with 15 ohm resistor load for the test system.

Sampling frequency: 17.24 kHz.

Fig. 10 Dynamic response under load change from 100% to 0% for the test system. Sampling frequency: 17.24 kHz.

Fig. 11 Dynamic response under load change from 0 % to 100 % for the test system. Sampling frequency: 17.24 kHz.

であった. 負荷急変時の出力電圧の過渡電圧変動波形を Fig. 10 および Fig. 11 に示す. 過渡電圧変動率は  $100\% \rightarrow 0\%$ の負荷急変時に + 10.5% (整定時間 160 msec.),  $0\% \rightarrow 100\%$ のときに - 9.7% (同 160 msec.) であった. 前項と同様のシミュレートの結果, Ud が 5 V 変化したとき, 出力電圧は実効値で 2.5 V (2.5%) の変化となることがわかった.

## 4.1.3 サンプリング周波数の影響

サンプリング周波数を 34.48~kHz から 17.24~kHz に低くすると、定常状態の歪率は、無負荷時で 2.51% から 2.97%、  $15~\Omega$  負荷時で 2.97% から 5.0% まで大きくなった、過渡電圧変動率は 8.15% から 10.5% に、整定時間も 100~msec. から 160~msec. になった、サンプリング周波数が低下すると、インバータの制御特性を低下させることがわかった。

#### 4.2 デッドタイム補償の効果

#### 4.2.1 サンプリング周波数 34.48 kHz での実験

4.1.1 項におけるパラメータに基づいて、デッドタイム補償を加えた. 15  $\Omega$ 負荷時の出力電流・電圧波形および出力電圧の FFT を、Fig. 12 および Fig. 13 にそれぞれ示す。デッドタイム補償を加えることによって出力電圧の歪率は 2.97% から 2.64% に改善された.

#### 4.2.2 サンプリング周波数 17.24 kHz での実験

4.1.2 項におけるパラメータに基づいて、デッドタイム補償を加えた. 15  $\Omega$ 負荷時の出力電流・電圧波形および出力電圧の FFT を、Fig. 14 および Fig. 15 にそれぞれ示す。デッドタイム補償を加えることによって出力電圧の歪率は 5.0%から 4.61% に改善された。これらの結果より、デッドタイム補償は、出力電

Fig. 12 The output waveform under the condition of dead-time compensation for the test system. Sampling frequency: 34.48 kHz.

Fig. 13 FFT under the condition of dead-time compensation for the test system. Sampling frequency: 34.48 kHz.

Fig. 14 The output waveform under the condition of dead-time compensation for the test system. Sampling frequency: 17.24 kHz.

Fig. 15 FFT under the condition of dead-time compensation for the test system. Sampling frequency: 17.24 kHz.

圧の歪率を減少させる効果があることがわかった.

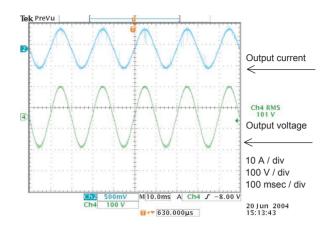

#### 4.3 出力電流補償の効果

4.1.1 項のパラメータを採用して、整流器負荷における出力電流補償の効果を確認した。Fig. 16 に出力電流補償を無効にした時の出力電流・電圧波形を、Fig. 17 にそれを有効にした時の結果を示す。また、Table 3 に出力電流補償の有無による特性の比較を示す。これより、出力電流補償が整流器負荷時の出力電圧波形の歪率を向上させるのに効果があることがわかる。

Fig. 16 The output waveforms under the condition of output current compensation with rectifier load for the test system.

Fig. 17 The output waveforms under the condition of output current compensation with rectifier load for the test system.

Table 3 Comparison of performance between two situations of output current compensation for the test system.

| Situation | tion Current  |              |                 | Voltage |              | Output power |          |

|-----------|---------------|--------------|-----------------|---------|--------------|--------------|----------|

|           | Peak<br>value | RMS<br>value | Crest<br>factor |         | RMS<br>value | Power        | Capacity |

|           | / A           | / A          | / %             | / %     | / V          | / W          | / VA     |

| Disable   | 12.6          | 4.58         | 2.75            | 5.5     | 100.2        | 315          | 459      |

| Enable    | 16.1          | 5.1          | 3.16            | 3.8     | 99.96        | 323          | 510      |

#### 5 まとめ

デジタル PID 制御をミニ UPS インバータに適用するために、実験システムを構成して、シミュレーションおよび実験をおこなった。その結果、制御特性はサンプリング周波数を低くすると敏感に低下すること、およびデットタイムによる誤差の補償は定常状態の制御特性を、出力電流補償は整流器負荷時の制御特性を向上させるのに有効であることがわかった。

以上の結果から、ミニ UPS 用インバータにデジタル制御が適用できる見通しが得られた。今後は、実用化に向けて、低いサンプリング周波数での制御特性の向上に取り組みたい。

#### 参考文献

- 坂根誠,山中雅雄,京博之,高田知明,ユアサ時報, 86,23 (1999).

- 2) K.Hirachi, M.Yamanaka, and M.Sakane, *Proc. of IEE-Japan IPEC 2000 Tokyo*, **2**, 976 (2000).